Аналоговый цифровой преобразователь с промежуточным буфером при высокой скорости поступления данных

В наше время большое распространение получили цифровые системы обработки сигналов. Для этого необходим преобразователь аналогового сигнала в цифровой код.

В данном проекте необходимо разработать быстродействующий аналого-цифровой преобразователь с временным буфером для хранения данных и преобразователь параллельного цифрового кода в последовательный цифровой код. Так же необходимо разработать систему управления данным преобразователем.

Данный курсовой проект посвящен разработке структурной и принципиальной схем такого преобразователя.

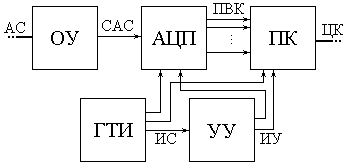

1. Структурная схема

Структурная схема преобразователя аналогового сигнала в последовательный код содержит следующие элементы:

ОУ – схема включения согласующего операционного усилителя

АЦП – аналого-цифровой преобразователь (преобразователь аналогового сигнала в параллельный восьмиразрядный код)

ПК – преобразователь параллельного восьмиразрядного кода в последовательный

ГТИ – задающий генератор тактовых импульсов

УУ – устройство управления преобразователем

Рис. 1. Структурная схема преобразователя

где

АС – аналоговый сигнал (напряжение Uвх)

САС – согласованный аналоговый сигнал

ПВК – параллельный восьмиразрядный код

ЦК – цифровой код (последовательный код)

ИС – импульсы синхронизации (тактовые импульсы)

ИУ – импульсы управления

2. Принципиальная схема

На основе структурной схемы была разработана принципиальная схема.

2.1 Выбор основной элементной базы

Генератор тактовых импульсов строится на микросхеме К155ЛА3 и кварцевом резонаторе ZQ1.

Счетчик импульсов представляет из себя микросхему К555ИЕ9.

Устройство управления строится на логических элементах – микросхемы К555ЛН1, К555ЛИ6 и К555ЛА2.

В качестве АЦП возьмем микросхему К1108ПВ1А.

Преобразователь параллельного кода в последовательный построим на микросхеме К555ИР9.

Схема сопряжения содержит операционный усилитель типа К574УД1.

В качестве линии связи используется 2-х проводная витая пара типа МГТФ.

Перечень элементов представлен в приложении.

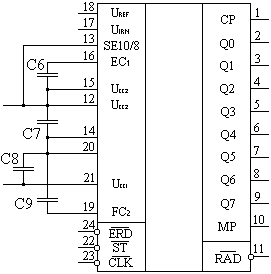

2.2 Аналого-цифровой преобразователь (АЦП)

Мы используем микросхему быстродействующего функционально законченного АЦП последовательного приближения К1108ПВ1А предназначенную для преобразования аналогового сигнала в двоичный параллельный цифровой код.

Микросхема рассчитана на преобразование однополярного входного напряжения в диапазоне от 0 до 3 В, при максимальной частоте преобразования 1,33 МГц для восьмиразрядного режима.

Для работы АЦП К1108ПВ1А требуется несколько внешних керамических конденсаторов и источники напряжения Ucc1 = 5 В ± 5% и Ucc2 = -5,2 В±5%. Мощность потребляемая от источников питания, не превышает 0,85 Вт. Конденсатор С9 необходим для частотной коррекции ОУ и фильтрации помех.

Для работы в восьмиразрядном режиме вход SE10/8 соединяется с шиной отрицательного источника питания Ucc2.

Цикл преобразования в режиме восьмиразрядного АЦП состоит из 10 тактов (восемь рабочих в процессе кодирования и по одному служебному в начале и конце цикла преобразования).

Цикл начинается с первым отрицательным фронтом тактового импульса после поступления команды ST. Во время первого служебного такта осуществляется сброс регистров и установление напряжения на входе селектора опорных уровней.

В течение следующих восьми тактов происходит кодирование аналогового сигнала при условии, что он зафиксирован на входе АЦП.

На десятом такте код из регистра хранения переписывается в выходной регистр, после чего формируется сигнал готовности данных. Появление на выходе RAD сигнала логический 0 свидетельствует о смене информации в выходном регистре и ее хранении весь следующий цикл преобразования.

Для считывания информации необходимо подать на вход ERD сигнал логический 0.

Запуск АЦП считается устойчивым, если сигнал ST подается в течение одного периода тактовой частоты с момента начала очередного цикла (t = 1 мкс).

К ТТЛ ЦИС микросхема К1108ПВ1А подключается без дополнительных устройств сопряжения.

Рис. 2. ИС К1108ПВ1А

Назначение выводов ИС К1108ПВ1А

1. Цифровой выход CP

2. Цифровой выход

3. Цифровой выход

4. Цифровой выход

5. Цифровой выход

6. Цифровой выход

7. Цифровой выход

8. Цифровой выход

9. Цифровой выход

10. Цифровой выход MP

11. Готовность данных RAD

12. Напряжение питания Ucc2

13. Укороченный цикл SE10/8

14. Общий (цифровая земля)

15. Напряжение питания Ucc2

16. Коррекция СУ EC1

17. Аналоговый вход UIRN

18. Внешний ИОН UREF

19. Коррекция ОУ ИОН FC2

20. Общий (аналоговая земля)

21. Напряжение питания Ucc1

22. Запуск ST

23. Тактовый вход CLK

24. Разрешение считывания ERD

Микросхема К1108ПВ1А имеет следующие характеристики

(Ucc1 = 5,25 В; Ucc1 = -5,25 В; U1вых ³ 2,4 В; U0вых £ 0,4 В; Iпотр сс1 £ 50 мА;

Iпотр сс2 £ 130 мА; I0вх £ 2,5 мА; I1вх £ 0,4 мА; I0вых ³ 3,2 мА; I1вых ³ 0,1 мА; tздр £ 60 нс)

Потребляемая мощность микросхемы К1108ПВ1А равна: Pпотр£850 мВт

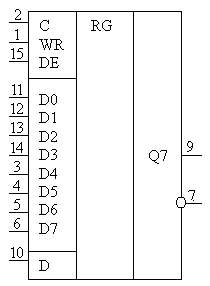

2.3 Преобразователь параллельного кода в последовательный код

Для этой цели используется восьмиразрядный сдвиговый регистр К555ИР9 (DD6). Этот регистр позволяет записывать параллельный восьмиразрядный код. Преобразование параллельного кода в последовательный происходит за восемь тактов подаваемых на синхронизирующий вход С. На первом такте подаваемом на вход С параллельный восьмиразрядный код записывается как Q0¸Q7 (Qi – состояние выхода i-го разряда), для этого подаем низкий потенциал на вход ®WR переключая тем самым регистр в режим записи. На первом такте значение Q7 передается на выход. На втором такте подаваемом на С параллельный код Q0¸Q7 сдвигается на один разряд Q0®Q1, Q1®Q2, …, Q6®Q7. Последовательный вход D® заземляем, поэтому в первый разряд записывается нуль (Q0 = 0). На выходе появляется следующий импульс. За восемь тактов весь код выходит из регистра последовательно. Вывод DE не используем и тоже заземляем.

Рис. 3. ИС К555ИР9

Назначение выводов ИС К555ИР9

1. Запись-чтение ®WR

2. Тактовый вход C

3. Вход D4

4. Вход D5

5. Вход D6

6. Вход D7

7. Инверсный выход Q7

8. Общий GND

9. Прямой выход Q7

10. Последовательный вход D®

11. Вход D0

12. Вход D1

13. Вход D2

14. Вход D3

15. Задержка такта DE

16. Питание Ucc

Таблица истинности ИС К555ИР9

Таблица 1

| Входы | Выходы | ||||||

| WR | DE | C | D® | D0-D7 | Q0 | Q1 | Q7 |

| L | X | X | X | d0-d7 | d0 | d1 | d7 |

| H | L | L | X | X | Q00 | Q10 | Q70 |

| L | H | X | H | Q0n | Q6n | |

| L | L | X | L | Q0n | Q6n | |

| H | H | X | X | X | Q00 | Q10 | Q70 |

Микросхема К555ИР9 имеет следующие характеристики

(Ucc = 5,25 В; U1вых ³ 0,5 В; U0вых ³ 2,4 В; Iпотр £ 20 мА; I0вх £ 0,4 мА; I1вх £ 0,02 мА;

I0вых ³ 8 мА; I1вых £ -2,6 мА; tздр £ 65 нс)

Потребляемая мощность микросхемы К555ИР9 равна: Pпотр = 105 мВт

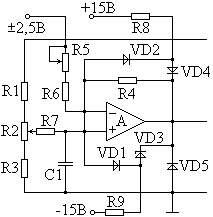

2.4 Схема включения согласующего операционного усилителя

Мы используем схему подключения согласующего операционного усилителя для преобразования двухполярного входного напряжения. В ней используется инвертирующий режим усиления (по отношению к Uвх) и диодная схем защиты АЦП при перегрузках. Напряжение на входе АЦП связано с входным сигналом следующим соотношением

UIRN = – K×Uвх + (1 + K)×UREF1

где K = R4/(R5 + R6) – коэффициент передачи усилителя

UREF1 – опорное напряжение на не инвертирующем входе ОУ (задается делителем R1-R3)

В нашем случае для диапазона преобразования Uвх = ±2,5В выбираются К = 0,58 и опорный уровень UREF1 = 0,905 В (при UREF = 2,5 В). Настройка коэффициента передачи осуществляется сопротивлением резистора R5, после чего резистором R2 устанавливается нуль на середину передаточной характеристики АЦП.

При Uвх =2,5В на АЦП появляется выходной код 00..00, а при Uвх=-2,5В – код 11..11.

Таким образом, на выходе преобразователя получаем обратный смещенный двоичный код.

Схема защиты входа АЦП от перегрузок работает следующим образом. Диоды VD1 и VD2, включенные параллельно резистору обратной связи R4, образуют двухсторонний ограничитель. Диод VD4 и стабилитрон VD3, смещенные постоянным током от источников 15 и –15В, задают уровни ограничения в отрицательной и положительной областях (относительно UREF1).

Диод VD5 обеспечивает защиту входа АЦП в случае отключения источников питания ОУ или выхода его из строя.

Данная схема включения согласующего ОУ универсальна и позволяет использовать АЦП К1108ПВ1А в режиме максимального быстродействия. При работе БИС АЦП с быстродействующим ОУ типа К574УД1, тщательном монтаже и оптимальной схеме коррекции ОУ время установления процессов в согласующей схеме на уровне 0,1% не превышает 1 мкс.

Рис. 4. Схема включения согласующего ОУ

В данной схеме используются следующие элементы:

VD1, VD2, VD4, VD5 – диоды типа КД520А

VD3 – стабилитрон типа КС133А

А – операционный усилитель типа К574УД1

Операционный усилитель типа К574УД1 имеет следующие характеристики

Ucc = ±15 В; Uвых ³ 10 мВ; Iвх £ 0,5 нА; Iпотр £ 10 мА

Потребляемая мощность составляет Pпотр = 150 мВт

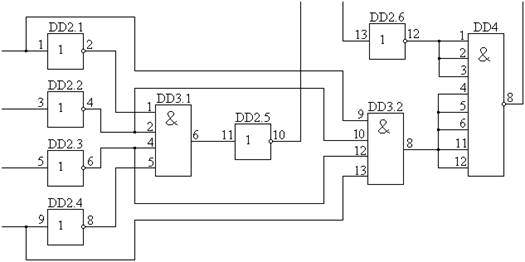

2.5 Схема управления АЦП и преобразователя кода

Схема управления (устройство управления) состоит из трех частей:

1. Генератор тактовых импульсов на кварцевом резонаторе

2. Двоично-десятичный счетчик

3. Схема управления на логических элементах «НЕ», «И» и «И-НЕ»

Для схемы управления мы используем следующие микросхемы: К555ИЕ9, К555ЛИ6, К555ЛН1, К555ЛА2 и К155ЛА3.

С генератора импульсов идут такты стабильной частоты. Они подаются на вход синхронизации двоично-десятичного счетчика. Счетчик производит счет от нуля до девяти. Полученный с выхода счетчика четырехразрядный код подается на логические элементы. Первый импульс подается на вход запуска АЦП приводя его в состояние готовности. Далее восемь тактов АЦП преобразует аналоговый сигнал со входа в параллельный восьмиразрядный код, а регистр в свою очередь преобразует параллельный восьмиразрядный код предыдущего цикла в последовательный код и выдает его в линию связи. На десятом такте с логических элементов идет сигнал на считывание кода с выхода АЦП и одновременно на регистр, для считывания следующего параллельного восьмиразрядного кода.

Все микросхемы синхронизированы одним тактовым генератором.

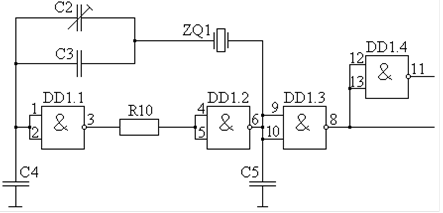

2.5.1 Генератор тактовых импульсов

В качестве генератора тактовых импульсов используем кварцевый автогенератор. Генератор строим на трех элементах «И-НЕ». Кварцевый генератор обеспечивает высокостабильный сигнал. Нестабильность выходного сигнала не превышает ±(5¸10)×10-6 в интервале температур 10¸40 0С. АЦП в восьмиразрядном режиме может работать на частоте до 1,3 МГц. Подберем такие емкости и резисторы, чтобы обеспечить нужную частоту. В нашем случае частота будет равна f = 1 МГц.

Рис. 5. Генератор тактовых импульсов

Так как на вход CLK АЦП нужно подавать инвертированный сигнал то он подключается к первому выходу генератора, а все остальные – ко второму выходу.

В схеме используются логические элементы «И-НЕ» микросхемы К155ЛА3, которые имеют следующие характеристики:

Назначение выводов ИС К155ЛА3

1. Вход данных

2. Вход данных

3. Выход данных

4. Вход данных

5. Вход данных

6. Выход данных

7. Общий GND

8. Выход данных

9. Вход данных

10. Вход данных

11. Выход данных

12. Вход данных

13. Вход данных

14. Питание Ucc

Рис. 6. ИС К155ЛА3

(Ucc = 5,25 В; U1вых ³ 2,4 В; U0вых £ 0,4 В; Iпотр £ 8,5 мА; I0вх £ 0,04 мА; I1вх £ 0,25 мА;

I0вых ³ 8 мА; I1вых £ -0,4 мА; tздр £ 19 нс)

Потребляемая мощность для одного логического элемента «И-НЕ» равна: Pпотр = 44,625 мВт

Суммарная потребляемая мощность микросхемы К155ЛА3 равна:

Pпотр сум = 178,5 мВт

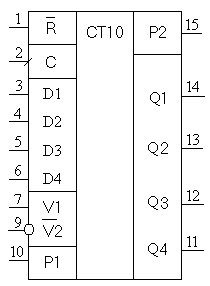

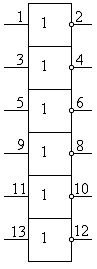

2.5.2 Счетчик импульсов

Используем микросхему К555ИЕ9 (DD7) четырехразрядный двоично-десятичный счетчик с асинхронным сбросом, дешифрующим счетным выходом, с возможностью асинхронной установки в произвольное состояние от нуля до девяти.

Данный счетчик является составной частью системы управления АЦП и преобразователя параллельного кода в последовательный. Его задача состоит в счете от 0 до 9, преобразование последовательности тактовых импульсов в параллельный четырехразрядный код, для последующего преобразования его ТТЛ логикой в сигналы управления.

Тактовые импульсы подаются с генератора на вход С. Он работает по переднему фронту входного импульса (0®1). Так как счетчик работает постоянно, то нас не интересует какое значение установится при его запуске, т.е. предварительный сброс счетчика в ноль не требуется, поэтому на вход R подадим потенциал высокого уровня.

Предварительная запись значения в счетчик по входам D1, D2, D3, D4 нас не интересует поэтому необходимо эти выводы микросхемы заземлить. Так как нет предварительной записи, то не требуется и вход разрешающий предварительную запись V2. На этот вывод подадим потенциал высокого уровня.

Вывод P2 выдает высокий уровень напряжения через каждые десять тактов, когда значение в счетчике равно девяти (Q1 = Q4 = 1; Q2 = Q3 = 0). В нашей схеме мы его не используем.

Вывод P1 используется для разрешения переноса импульса в следующий каскад (если соединяются несколько счетчиков последовательно). У нас только один счетчик поэтому на вывод P1 должно постоянно подаваться напряжение высокого уровня. На вход разрешения счета V1 так же должно подаваться напряжение высокого уровня.

Выводы P1, V1, V2, R – подаем высокий уровень напряжения

Выводы D1, D2, D3, D4 – заземляем

Назначение выводов ИС К555ИЕ9

1. Вход «установка L» R

2. Вход синхронизации С

3. Вход информационный D1

4. Вход информационный D2

5. Вход информационный D3

6. Вход информационный D4

7. Вход разрешения счета V1

8. Общий GND

9. Вход разрешения предварительной записи V2

10. Вход разрешения переноса P1

11. Выход четвертого разряда Q4

12. Выход третьего разряда Q3

13. Выход второго разряда Q2

14. Выход первого разряда Q1

15. Выход переноса

16. Питание Ucc

Рис. 7. ИС К555ИЕ9

Таблица 2. Таблица рабочих состояний ИС К555ИЕ9

Входы | Выходы | Состояние | |||||

| R | V2 | V1 | P1 | C | D1-D4 | Q1-Q4 | |

| L | X | X | X | X | X | L | Установка в L |

| H | L | X | X | D | D | Предварит. запись | |

| H | H | H | H | X | Y+1 | Счет (+1) | |

| H | H | L | X | X | X | Q (n-1) | Запрет счета (хранение) |

| H | H | X | L | X | X | ||

где Y – двоичный код предыдущего состояния

Таблица 3. Таблица истинности ИС К555ИЕ9

Вход | Выходы | ||||

| P1 | Q4 | Q3 | Q2 | Q1 | P2 |

| L | H | X | X | H | L |

| H | H | X | X | H | H |

| X | Любой код меньше 9 | L | |||

Микросхема К555ИЕ9 имеет следующие характеристики

(Ucc = 5,25 В; U1вых ³ 2,7 В; U0вых £ 0,5 В; Iпотр £ 31 мА; I0вх ³ -0,4 мА; I1вх £ 0,02 мА;

I0вых ³ 8 мА; I1вых £ -0,4 мА; tздр £ 39 нс)

Потребляемая мощность микросхемы К555ИЕ9 равна: Pпотр = 162,75 мВт

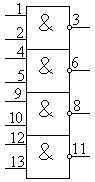

2.5.3 Устройство управления на логических элементах

Четырехразрядный код с двоично-десятичного счетчика подается на логические элементы. Если код равен нулю, то срабатывает первый элемент «И» (DD3.1) и импульс подается на АЦП, на вход запуска ST. Так как с элемента «И» (DD3.1) импульс идет не инвертированный, то перед ST необходимо поставить инвертор – логический элемент «НЕ» (DD2.5).

Если на выходе счетчика появляется код равный девяти, то срабатывает второй элемент «И» (DD3.2). Подаем импульс с выхода «И» (DD3.2) сразу на пять входов элемента «И-НЕ» (DD4). Это совпадает с выходом на выводе RAD АЦП логического нуля. Инвертируем этот импульс элементом «НЕ» (DD2.6) и подаем на три оставшихся входа элемента «И-НЕ» (DD4). Инвертированный импульс подается сразу на два вывода, на вывод ERD считывания данных с АЦП и вывод записи ®WR регистра.

Рис. 8. Устройство управления на логических элементах

Устройство управления на логических элементах содержит следующие микросхемы: К555ЛН1, К555ЛИ6, К555ЛА2

Рис. 9. ИС К555ЛН1

Назначение выводов ИС К555ЛН1

1. Вход данных

2. Выход данных

3. Вход данных

4. Выход данных

5. Вход данных

6. Выход данных

7. Общий GND

8. Выход данных

9. Вход данных

10. Выход данных

11. Вход данных

12. Выход данных

13. Вход данных

14. Питание Ucc

Микросхема К555ЛН1 (инвертор) имеет следующие характеристики

(Ucc = 5,25 В; U1вых ³ 2,7 В; U0вых £ 0,5 В; Iпотр £ 2,4 мА; I0вх ³ -0,36 мА; I1вх £ 0,02 мА;

I0вых ³ 8 мА; I1вых £ -0,4 мА; tздр £ 28 нс)

Потребляемая мощность для одного логического элемента «НЕ» равна:

Pпотр = 12,6 мВт

Суммарная потребляемая мощность микросхемы К555ЛН1 равна:

Pпотр сум = 75,6 мВт

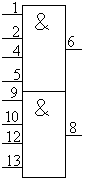

Рис. 10. ИС К555ЛИ6

Назначение выводов ИС К555ЛИ6

1. Вход данных

2. Вход данных

3. Выход данных

4. Вход данных

5. Вход данных

6. Не используется

7. Общий GND

8. Выход данных

9. Вход данных

10. Вход данных

11. Не используется

12. Вход данных

13. Вход данных

14. Питание Ucc

Микросхема К555ЛИ6 имеет следующие характеристики

(Ucc = 5,25 В; U1вых ³ 2,7 В; U0вых £ 0,5 В; Iпотр £ 2,4 мА; I0вх ³ -0,36 мА; I1вх £ 0,02 мА;

I0вых ³ 8 мА; I1вых £ -0,4 мА; tздр £ 24 нс)

Потребляемая мощность для одного логического элемента «И» равна:

Pпотр = 12,6 мВт

Суммарная потребляемая мощность микросхемы К555ЛИ6 равна:

Pпотр сум = 25,2 мВт

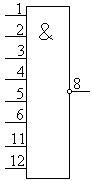

Назначение выводов ИС К555ЛА2

Рис. 11. ИС К555ЛА2

1. Вход данных

2. Вход данных

3. Вход данных

4. Вход данных

5. Вход данных

6. Вход данных

7. Общий GND

8. Выход данных

9. Не используется

10. Не используется

11. Вход данных

12. Вход данных

13. Не используется

14. Питание Ucc

Микросхема К555ЛА2 имеет следующие характеристики

(Ucc = 5,25 В; U1вых ³ 2,7 В; U0вых £ 0,5 В; Iпотр £ 0,5 мА; I0вх ³ -0,4 мА; I1вх £ 0,02 мА;

I0вых ³ 8 мА; I1вых £ -0,4 мА; tздр £ 28 нс)

Потребляемая мощность микросхемы К555ЛА2 равна:

Pпотр = 2,625 мВт

Общая потребляемая мощность устройства управления на логических элементах равна: Pпотр рез = 103,425 мВт

3. Конструктивное исполнение системы

Все микросхемы и элементы системы преобразования и управления монтируются на стандартной печатной плате. В качестве материала для печатной платы используется фольгированный текстолит либо гетинакс.

Питание в виде +5,25 В, -5,25 В, +15 В, -15 В подаётся по разъёму XS1 ко всем микросхемам через конденсаторные фильтры для предохранения элементов от сгорания вследствие перепадов напряжения.

Микросхемы располагаются по координатной сетке с шагом, соответствующим шагу между выводами микросхем.

Для предотвращения окисления контактов, печатная плата покрывается нитролаком либо канифольным лаком.

Заключение

В результате проделанной работы мы получили высокоскоростной преобразователь аналогового сигнала в цифровой код. Были разработаны структурная и принципиальная схемы преобразователя, а так же системы управления преобразователя. Принципиальная схема содержит 7 микросхем, 1 операционный усилитель, 5 диодов, 10 резисторов, 9 конденсаторов, 1 кварцевый резонатор. Все элементы являются хорошо распространенными и доступными для использования.

Список литературы

1. Федорков Б.Г., Телец В.А. Микросхемы ЦАП и АЦП: функционирование, параметры, применение. - М.; Энергоатомиздат, 1990.

2. Ерофеев Ю.Н. Импульсные устройства. - М.; Высшая школа, 1989.

3. Шило В.Л. Популярные цифровые микросхемы.-М.; Радио и связь, 1987.

4. Мальцев П.П., Долидзе Н.С., Критенко М.И. Цифровые интегральные микросхемы: Справочник.-М.; Радио и связь, 1994.

5. Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ: Справочник.-М.; Машиностроение, 1993.

6. Гусев В.Г., Гусев Ю.М. Электроника. - М.; Высшая школа, 1991.

7. Интегральные микросхемы: Справочник / Б.В. Тарабрин, Л.Ф. Лунин, Ю.Н. Смирнов и др.; Под ред. Б.В. Тарабрина. - М. Радио и связь, 1984.

8. Справочник по полупроводниковым диодам, транзисторам и интегральным схемам / Под ред. Н.Н. Горюнова. - М.; Энергия, 1977.

Категории:

- Астрономии

- Банковскому делу

- ОБЖ

- Биологии

- Бухучету и аудиту

- Военному делу

- Географии

- Праву

- Гражданскому праву

- Иностранным языкам

- Истории

- Коммуникации и связи

- Информатике

- Культурологии

- Литературе

- Маркетингу

- Математике

- Медицине

- Международным отношениям

- Менеджменту

- Педагогике

- Политологии

- Психологии

- Радиоэлектронике

- Религии и мифологии

- Сельскому хозяйству

- Социологии

- Строительству

- Технике

- Транспорту

- Туризму

- Физике

- Физкультуре

- Философии

- Химии

- Экологии

- Экономике

- Кулинарии

Подобное:

- Ансамбли различаемых сигналов. Структура устройств распознавания портретов. Оптимальная обработка некоррелированных портретов

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИкафедра ЭТТРЕФЕРАТ на тему:«Ансамбли различаемых сигналов. Ст

- Антени військових радіостанцій

Антени військових радіостанційЗагальні положенняАнтенами називаються пристрої, призначені для випромінювання і прийому електромагні

- Антенна РЛС – параболоид вращения

1. ПРИНЦИП ДЕЙСТВИЯ ПАРАБОЛИЧЕСКОЙ АНТЕННЫ2. ВЫБОР ГЕОМЕТРИЧЕСКИХ РАЗМЕРОВ ПАРАБОЛИЧЕСКОГО ЗЕРКАЛА3. ВЫБОР ОБЛУЧАТЕЛЯ, И ЕГО РАСЧЕТ3.1. По

- Аперіодичний підсилювач безперервних коливань

Аперіодичний підсилювач безперервних коливаньЗміст1. Особливості підстлювачів з СБ, СК та порівняльний аналіз схем (каскадів) підсилен

- Аппарат для ультразвуковой терапии: обобщенная структура, применение ультразвука в хирургии

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИКафедра ЭТТРЕФЕРАТНа тему:"Аппарат для ультразвуковой терапии

- Аппаратно-студийный комплекс областного телецентра

Целью данной работы является получения навыков при расчете и разработке АСК с изготовлением видеопрограмм на кассетах, умения применят

- Аппаратура для терапии постоянным и НЧ током

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИкафедра ЭТТРЕФЕРАТ на тему: "АППАРАТУРА ДЛЯ ТЕРАПИИ ПОСТОЯННЫМ

www.referat-web.com Бесплатно скачать - рефераты, курсовые, контрольные. Большая база работ.

www.referat-web.com Бесплатно скачать - рефераты, курсовые, контрольные. Большая база работ.